はじめに:見過ごされがちな「メモリ管理」という名の最重要インフラ

現代のコンピューティングシステムにおいて、セキュリティと効率は永遠の課題です。特に、一つの物理的なハードウェア上で複数の独立した環境(仮想マシンやコンテナ)を動作させる仮想化技術が主流となる中で、これらの課題はより複雑化しています。クラウドコンピューティング、エッジAI、そして機密データを扱うあらゆるアプリケーションの基盤は、この仮想化技術の上に成り立っています。

しかし、この仮想化の「陰」で、システムの安定性とセキュリティを根底から支えている技術があります。それが「メモリ管理」です。

アプリケーションが動作するために不可欠なメモリは、OSやハイパーバイザによって細心の注意を払って割り当てられ、保護されなければなりません。特に、機密性の高い処理を行うための「セキュア環境」を確保する技術は、次世代コンピューティングの中核を担っています。

近年、このセキュアな仮想化環境を実現しつつ、パフォーマンスのボトルネックを解消しようとする、極めて専門的で先鋭的な技術が多数登場しています。本稿では、そんな特許情報から垣間見える、次世代のコンピューティングを支えるセキュアなメモリ管理技術、特にARM64アーキテクチャなどで用いられる二段階アドレス変換(Two-Stage Address Translation)と、それを効率化するTLB(Translation Lookaside Buffer)インバリデーション(無効化)の進化に焦点を当てます。

その核心にあるのは「いかにして速く、そして絶対的に安全に、メモリをアプリに割り当てるか」というシンプルかつ究極の問いです。

1. なぜ「セキュアな仮想化」が求められるのか:信頼の境界線

1-1. クラウド時代の絶対命題:マルチテナンシーと分離

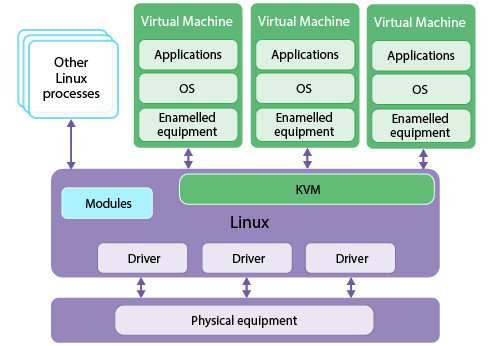

私たちが日常的に利用するクラウドサービスは、「マルチテナンシー」を前提としています。これは、一つの巨大な物理サーバー上で、無数の異なるユーザー(テナント)の仮想マシンが同時に稼働している状態を指します。

この環境で最も重要なのは、「テナント間の絶対的な分離」です。あるユーザーの機密データが、隣で稼働している別のユーザーの仮想マシンから覗き見られたり、干渉されたりすることは許されません。この分離を確実にするために、ハイパーバイザ(仮想化を実現するソフトウェア)や、よりセキュアな保護されたカーネルベース仮想マシン (pKVM; Protected Kernel-based Virtual Machine) のような技術が採用されます。

pKVMは、ゲストOS(ゲストアプリケーションが動作するOS)に割り当てられたメモリ領域を、ホストOS(ハイパーバイザ自身や、その上で動く管理用OS)からも保護することを目的としています。これは、ホストOSやハイパーバイザに脆弱性があったとしても、ゲストの機密データが漏洩しないようにするための「深度防御(Defense in Depth)」の考え方に基づいています。

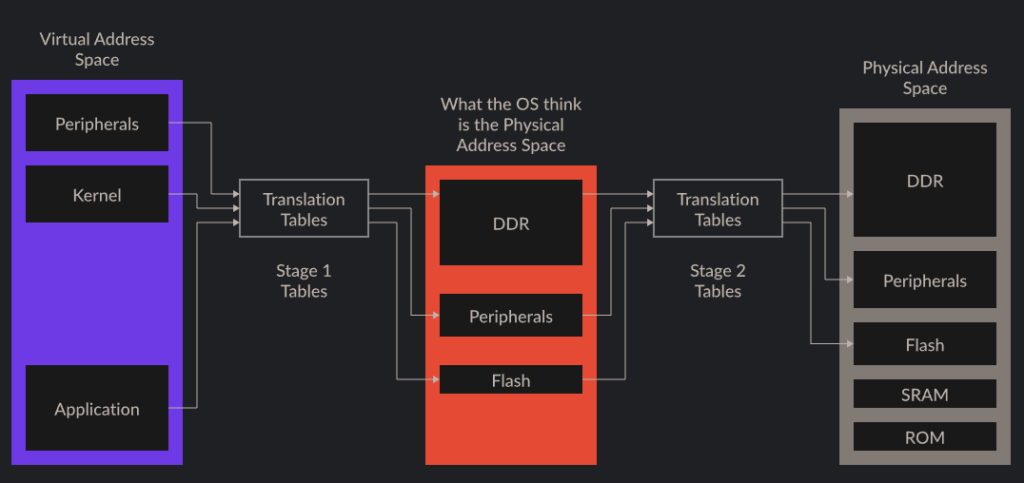

1-2. 鍵となる概念:仮想アドレス・IPA・物理アドレス

このセキュアな分離を実現するために、現代のMMU(Memory Management Unit)は、複雑な階層構造を用いてアドレス変換を行います。

| アドレス空間 | 定義と役割 |

| 仮想アドレス (Virtual Address, VA) | ゲストアプリケーションが認識するアドレス。無限大に見える空間。 |

| 中間物理アドレス (Intermediate Physical Address, IPA) | MMUの第一段階変換後のアドレス。ゲストOSはこれを「物理アドレス」と錯覚する。 |

| 物理アドレス (Physical Address, PA) | 実際のDRAM(物理メモリ)上のアドレス。ホスト側(MMU第二段階)が管理。 |

二段階アドレス変換:

- 第1段階 (Stage 1 MMU):ゲストアプリケーションのVAを、ゲストOSが認識するIPAに変換。

- 第2段階 (Stage 2 MMU):ホストシステム(ハイパーバイザ)が、そのIPAをPAに変換し、実際の物理メモリにアクセス。

pKVMなどのセキュア環境では、ゲストに割り当てるメモリを「保護された」領域として確保する際、ホスト側の第2段階マッピングからそのPAへのアクセスを解除または制限します。これにより、ホストOSが誤って、または悪意を持ってゲストのメモリ領域にアクセスすることを防ぎます。

2. TLBと物理アドレスベースの進化

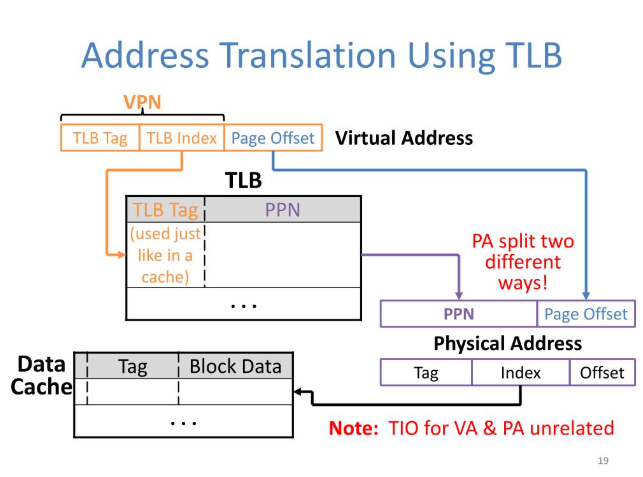

2-1. TLB:アドレス変換の高速キャッシュ

アドレス変換(VA → PA)は、システムがメモリにアクセスするたびに発生する必須の処理です。しかし、この変換テーブルは非常に大きく、メインメモリに格納されているため、毎回アクセスしていては性能が著しく低下します。

そこで登場するのが、TLB (Translation Lookaside Buffer) です。

TLBは、MMU内部に存在する高速なキャッシュメモリであり、最近使用されたVAとPAの変換ペアを一時的に保持します。これにより、ほとんどのメモリ参照において、MMUはTLB内の情報を利用して即座にPAを特定できるため、変換処理のレイテンシ(遅延)を劇的に短縮できます。

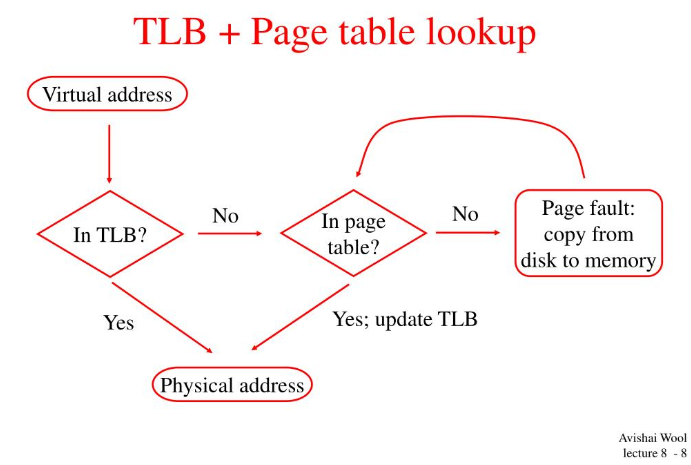

2-2. 変換情報の更新と「TLBインバリデーション」

問題は、メモリのマッピングが変更されたとき、つまり「VAとPAの対応」が変わったときに発生します。

たとえば、OSがメモリ領域を解放したり、再配置したりする際、TLB内に古い(誤った)マッピング情報が残っていると、アプリケーションは誤ったメモリ領域にアクセスしてしまいます。これはセキュリティ上の致命的な欠陥や、システムのクラッシュを引き起こします。

そのため、マッピングを変更した際は、TLB内の古いエントリを無効化(Invalidation) する処理が必要です。これを「TLBインバリデーション」と呼びます。

2-3. 物理アドレスベースのTLBインバリデーション

従来の仮想化環境では、TLBのインバリデーションは主に仮想アドレス(VA) または中間物理アドレス(IPA) をキーとして実行されていました。

しかし、セキュアな仮想化環境、特にゲストメモリをホストから保護するために、ホストOSの第2段階マッピングを解除するような場面では、従来のインバリデーション手法では非効率または不確実になる場合があります。

この技術の核心は、このインバリデーションを物理アドレス(PA) をベースに行う点にあります。

技術的なメリット:

- 確実な分離とクリーンアップ: ゲストアプリケーションに保護されたメモリ(PA) を割り当てた際、ホストOSのTLB内に、そのPAに紐づく古いVA/IPAマッピング情報が残っている可能性があります。PAベースでインバリデーションを行うことで、「この物理メモリ領域にアクセスしていた(ホスト側の)全てのエントリ」を確実にTLBから排除できます。これは、先に述べた「ホストからのアクセス制限」をハードウェアレベルで完全に反映させるために不可欠です。

- アドレス空間の独立性: VAやIPAは、環境やプロセスごとに異なる空間ですが、PAは物理メモリを一意に示すため、インバリデーション処理がシンプルかつ、環境(コンテキスト)に依存しない形で実行できます。

- 効率的な処理: 特定のPA範囲だけを指定してインバリデーションを実行できれば、TLB全体をフラッシュ(全無効化)するよりもオーバーヘッドが少なく、他の仮想マシンやプロセスのパフォーマンスに与える影響を最小限に抑えられます。

PAベースのTLBインバリデーションは、メモリ管理がもたらすセキュアな分離を、パフォーマンスを犠牲にすることなく実現するための、極めて重要な「微細な技術革新」なのです。これは、数ミリ秒、数ナノ秒の遅延すら許されない次世代のAI/ML処理やリアルタイムシステムにおいて、セキュリティと速度を両立させるための「見えないインフラストラクチャ」と言えます。

3. 次世代コンピューティングへの応用と未来

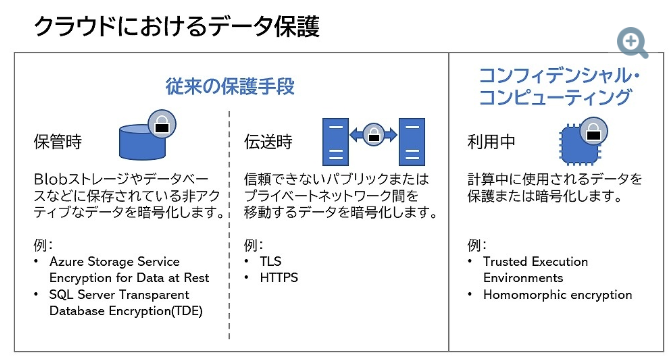

3-1. 機密コンピューティング (Confidential Computing) の実現

本技術は、機密コンピューティング(Confidential Computing) のトレンドと深く結びついています。機密コンピューティングとは、データが「使用中(In Use)」の状態、つまりCPU上で処理されている最中も保護されることを目指す技術分野です。

pKVMのようなセキュア仮想化技術と、PAベースのTLB管理は、ハードウェア・レベルでデータの機密性を保証するための基本的な構成要素となります。これにより、金融取引、医療データ解析、AIモデルの学習といった機密性の高いワークロードを、パブリッククラウドのような「信頼できない」環境でも安心して実行できるようになります。

3-2. ハードウェアとソフトウェアの協調の進化

この技術は、MMUのアーキテクチャ(ハードウェア)とOS/ハイパーバイザのメモリ管理ルーチン(ソフトウェア)の緊密な連携によって成り立っています。今後、セキュリティの脅威が高度化するにつれて、MMUやTLBといった低レイヤーのハードウェア機構に、より複雑でインテリジェントなセキュリティ・プリミティブ(基本機能) が組み込まれることが予想されます。

「物理アドレスベースのTLBインバリデーション」は、その進化の明確な一歩であり、セキュアなメモリ割り当ての瞬間に、ホストOSの残骸(TLBエントリ)を迅速かつ正確に一掃する「デジタルな掃除屋」の役割を果たしているのです。

結論:見えないところで進化する「安全」と「速度」

一見すると難解な技術用語の羅列に見えますが、その中には常に「現実の課題をいかに解決するか」というエンジニアの情熱と、未来のコンピューティングを形作るアイデアが詰まっています。

メモリ管理という、普段は意識されることのないレイヤーにおいて、「物理アドレスベースのTLBインバリデーション」のような緻密な技術革新が進んでいることは、次世代のセキュアで高性能なコンピューティング環境が着実に構築されている証拠です。

数多くの仮想マシンが、互いに完全に分離されながら、物理ハードウェアの力を最大限に引き出す未来は、これらの見えない技術によって支えられています。私たちが享受するクラウドサービスのセキュリティと快適さは、このような積み重ねの上に成り立っているのです。

参考文献 (Google Patents)

Google Patents (関連特許文献)

本記事の内容に関連する、セキュアな仮想化環境、メモリ管理、およびTLBインバリデーションに関する特許文献を以下に示します。これらは、セキュアな分離と効率的な処理を両立させるための技術開発の方向性を示しています。

- Methods and Apparatus for Efficient Resolution of Translation Lookaside Buffer Invalidations in a System-on-Chip

- 文献番号(例): US10783021B2

- 概要: 複数の処理ユニットが関与する環境において、TLBエントリの無効化を効率的に処理するためのメカニズムに関する特許。並列処理環境でのTLBコヒーレンシ(一貫性)の課題解決を目的としている。

- System and Method for Managing Memory Access in a Virtualized Environment

- 文献番号(例): US10204123B2

- 概要: 仮想マシン(ゲスト)のメモリアクセス要求を、ホスト(ハイパーバイザ)のMMUを介して効率的かつセキュアに処理するための技術。特に二段階アドレス変換におけるアクセス制御と例外処理の最適化に焦点を当てている。

- Memory Protection in a Secure Virtual Machine Environment

- 文献番号(例): US11755100B2

- 概要: 機密性の高いデータを持つセキュアなゲスト仮想マシンを、ホストOSの不正なアクセスから保護するためのメモリ管理とページテーブル設定に関する特許。物理的なメモリをセキュアと非セキュアに分離する技術が関わっている。

一般技術参照文献 (General Technical References)

特許文献に加え、本記事で議論した概念の基礎となる技術資料を以下に示します。

- ARM Architecture Reference Manual (ARMv8-A以降)

- 文脈: メモリ管理ユニット(MMU)、二段階アドレス変換(Stage 1およびStage 2)、およびTLB(Translation Lookaside Buffer)とその無効化メカニズム(TLBI命令)に関する公式仕様を提供します。pKVMのような技術の基盤となるアーキテクチャです。

- Kernel-based Virtual Machine (KVM) ドキュメンテーション

- 文脈: Linux向けのオープンソース仮想化インフラストラクチャであり、pKVM(Protected KVM)のような技術の基礎を提供します。KVMがどのようにゲストメモリを管理し、ハードウェア仮想化拡張機能と連携するかを詳述しています。

- Confidential Computing Consortium (CCC) 資料

- 文脈: 機密コンピューティング(Confidential Computing) に関する業界の定義やホワイトペーパーを提供しており、使用中のデータを保護する必要性、およびハードウェアベースのトラステッド実行環境(TEE)や保護された仮想化技術がこの目標を達成する上で果たす役割について説明しています。